ELSYS Eastern Europe provides high quality IC design and verification service, worldwide, ranging from ASIC to the most complex SoC design. Some of the biggest companies in the world entrusted us with their most difficult projects.

It is a sustained effort not to let our clients down. For two decades now we aim to be that one thing they don’t really have to worry about. We are looking forward to be a part of the solution for your company as well. We are a stable supplier, resilient to fluctuations of our clients’ external needs, with strong quality control and years of experience. As Ernest Hemingway once said: “The best way to find out if you can trust somebody – is to trust them.”

Rapid technological advances in the last 30 years have created increasingly complex digital systems. Good architecture development with review of reusability became one of the key factors for a good digital design. Read more

Design Verification is one of the most important aspects of the IC development process, consuming 60 – 80% of the total IC development resources and time. EEE offers a wide range of solutions in pre-silicon design verification that will allow fast and reliable product development for our customers. Read more

AMS verification focuses on verification of the analog/mixed-signal part of the chip, ensuring that every analog module, their mutual connections as well as connections to the digital core are working and verified properly. There are a couple of approaches to the mixed-signal verification, some focused on digital, some on analog side, but they all ensure that the verification job is well executed and finished successfully. Read more

Industries we support

Automotive

5G

IoT

Medical

Multimedia

Security

Transportation

Wireless

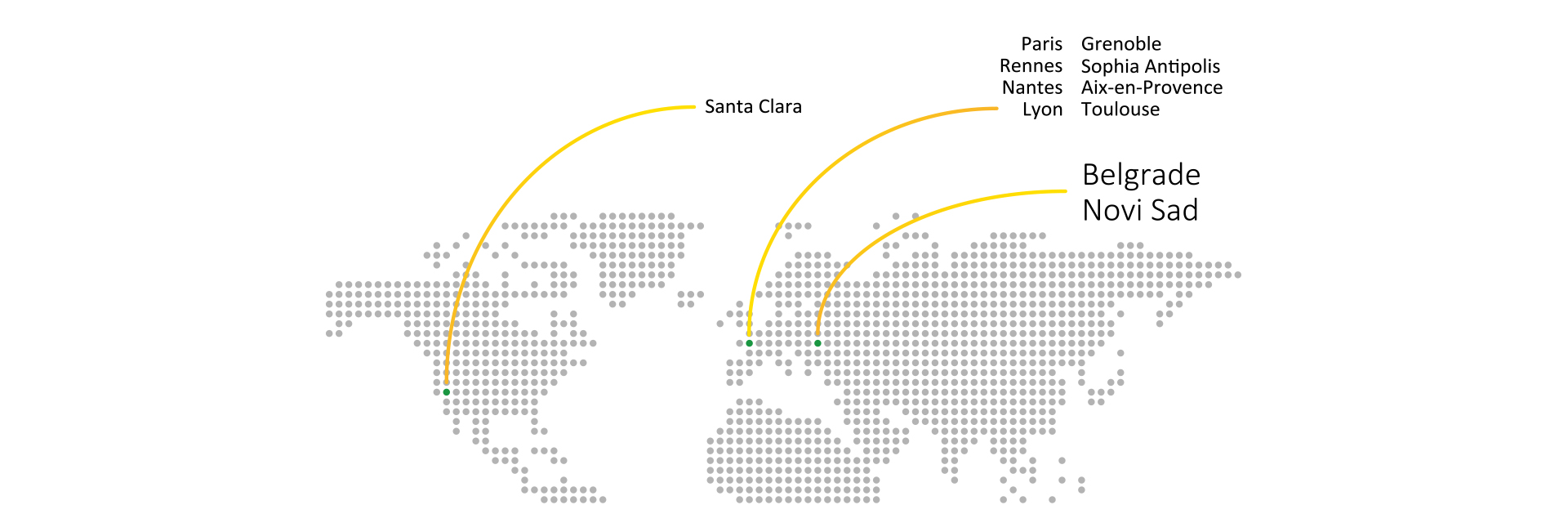

YEAH, WE’RE FROM EASTERN EUROPE

And you know what that means – it means we make things happen!

Honestly, we are as smart as everybody else, but as your future business partners we are in a favorable position and time zone, able to connect and simultaneously cater to US, Europe, Middle East, India and Japan. With an internal training center and strong talent sourcing we bring the brightest problem-solving, bug-catching minds to tackle your projects. Or we can assemble a dedicated team to provide you with an ongoing support.